Low jitter frequency synthesizers are required to achieve high data-rates in modern wireless and wireline transceivers. When battery powered devices utilize these synthesizers their power consumption must be limited, leading to complex design challenges.

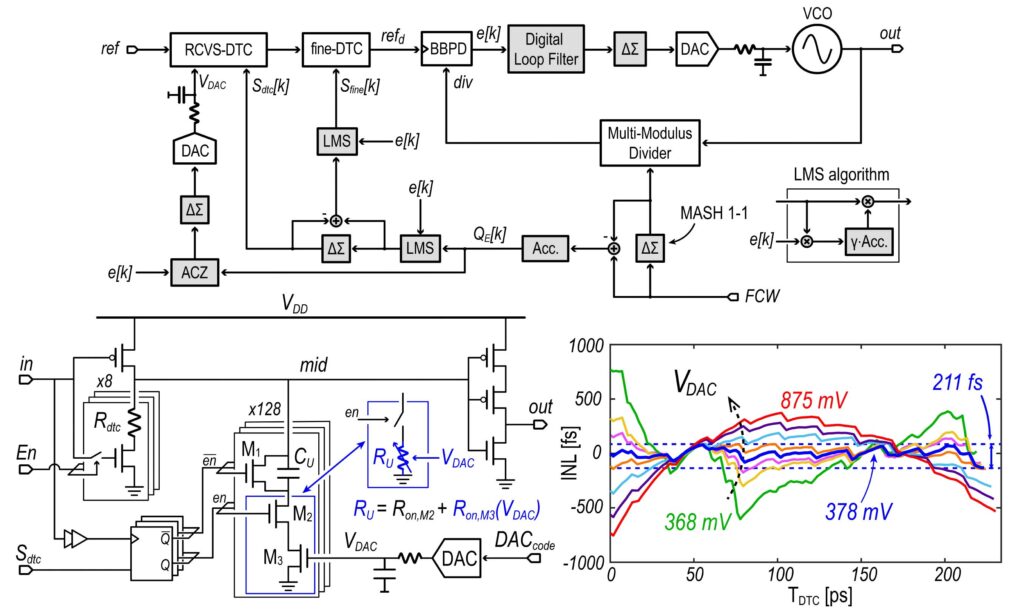

In our latest article we unveil the design of a fractional-N digital PLL that achieves sub-60fs rms jitter while dissipating only 17.5mW, leading to best-in-class power efficiency among ultra-low-jitter fractional-N PLLs.

These performance have been obtained by adopting a novel digital-to-time converter architecture, capable to provide an highly linear controllable delay with both low noise and low power consumption.

If you are interested in the topic please consider checking it out.