We are thrilled to share our latest work on TI ADCs.

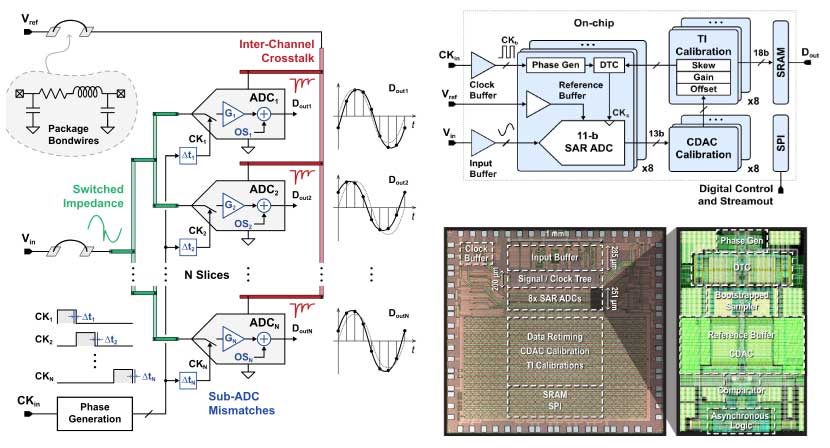

This design demonstrates that high-speed TI ADC design requires focus on auxiliary circuits and the sub-ADC to reduce the degradation of single-channel performance in interleaved mode.

Our paper proposes a 2-GSps TI ADC implemented in a 28-nm bulk CMOS process. The ADC interleaves eight 11-bit 250 MS/s SAR ADCs. It achieves a 9.2-ENOB and a 70.1-dB SFDR close to the Nyquist frequency. On a 1-GHz bandwidth, the TI ADC SNDR degrades only by 1.76 dB compared to the sub-ADC performance.

You might find the paper interesting if you’re working on TI ADC! Check out the article on early access in the IEEE Journal of Solid-State Circuits for all the details.

This work was made possible thanks to the collaboration of Politecnico di Milano with Infineon Technologies, Villach.

[URL]