In high-performance fractional-N frequency synthesizers, fractional spurs are a critical bottleneck—especially at near-integer channels—degrading both jitter and spectral purity. With next-generation wireless transceivers targeting extremely low jitter (below 80fs), effective spur mitigation becomes essential, often requiring suppression below –60 dBc.

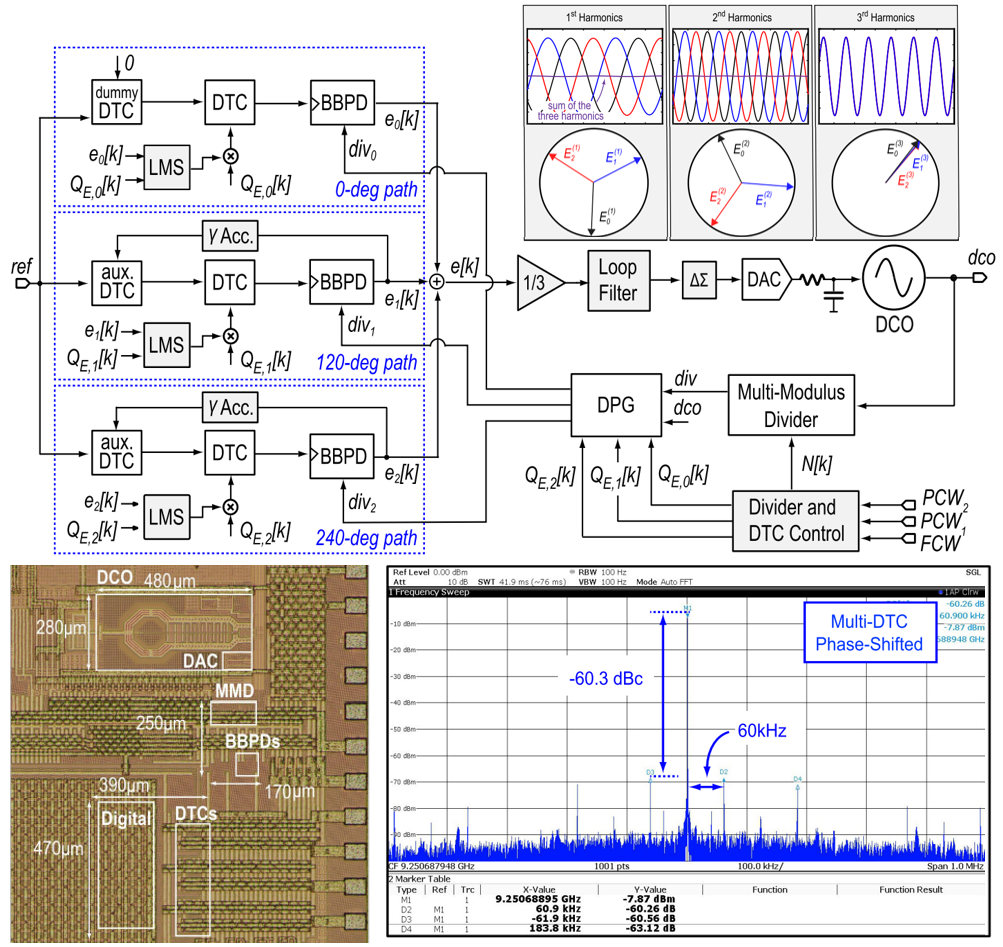

In our latest work, we present the design of a 10GHz digital fractional-N PLL that achieves sub-80fs rms jitter with in-band fractional spurs below -60dBc at near-integer channels.

The key enabler is a novel phase detection architecture with multiple parallel paths, comprising each a digital-to-time converter and a phase-detector, allowing fractional spur cancellation without increasing PLL in-band noise.

If you’re working on low-jitter clocking or next-gen transceivers, we invite you to check it out!