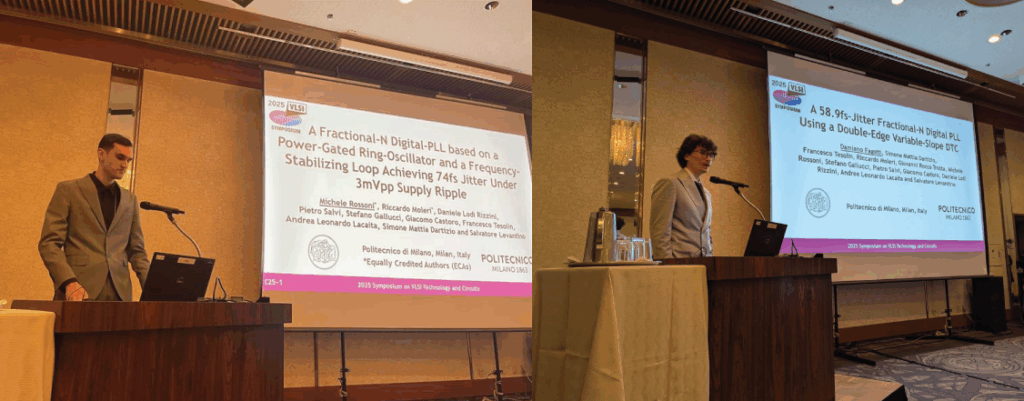

We are pleased to share that two of our PhD students presented their research at the VLSI Symposium 2025 in Kyoto.

Michele Rossoni presented “A Fractional-N Digital-PLL based on a Power-Gated Ring-Oscillator and a Frequency-Stabilizing Loop Achieving 74fs Jitter Under 3mVpp Supply Ripple”

Damiano Fagotti presented “A 58.9fs-Jitter Fractional-N Digital PLL Using a Double-Edge Variable-Slope DTC”

Congratulations to the ARPLab RF team for this achievement, and sincere thanks to the VLSI Symposium Secretariat for organizing an outstanding conference.