We are very proud to announce that, for the first time, three works from our laboratory ARPLab – DEIB, Politecnico di Milano, have been accepted for presentation at the International Solid-State Circuits Conference (ISSCC) 2026.

If you are planning to attend ISSCC in San Francisco next week, don’t miss the following presentations from our PhD candidates:

Tuesday, February 17th – Session 11: “Pipeline and Ultra-High-Speed Data Converters”

Michele Rocco will present:

“A 500MS/s 12b Pipe-SAR ADC Using a Triple-Cascode FIA with Virtual Supply Extension.”

Tuesday, February 17th – Session 12: “Frequency Synthesizers and VCOs”

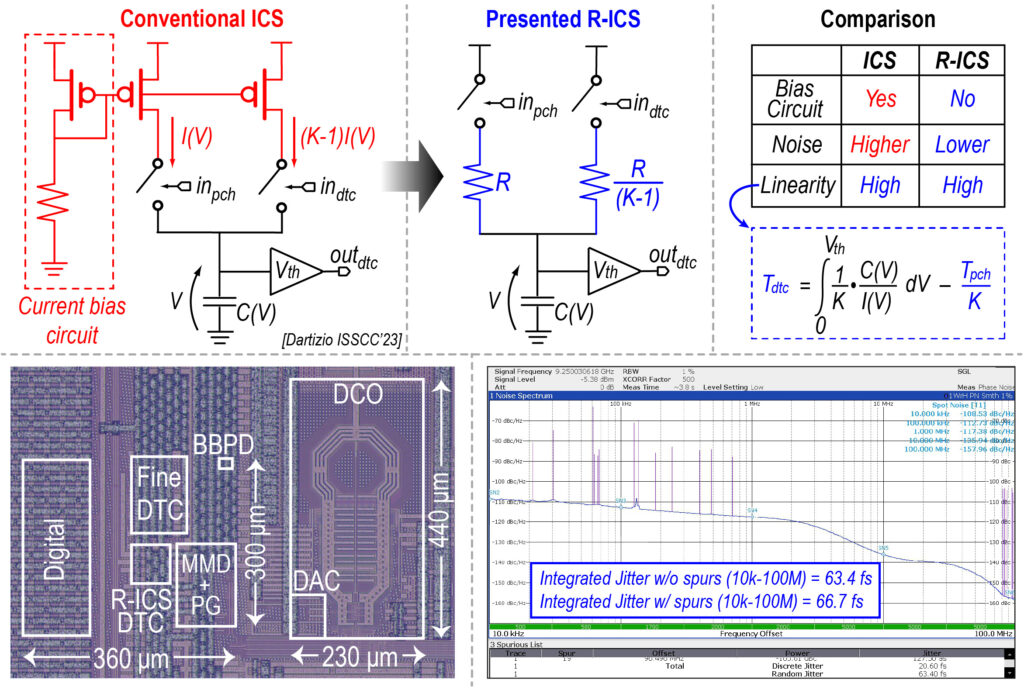

Damiano Fagotti will present:

“A Fractional-N Digital PLL with a Supply-Insensitive DTC Achieving –62dBc Spur and 69fs Jitter Under 10mVpp Sinusoidal DTC Supply Ripple and 6.2mVrms DTC Supply Noise.”

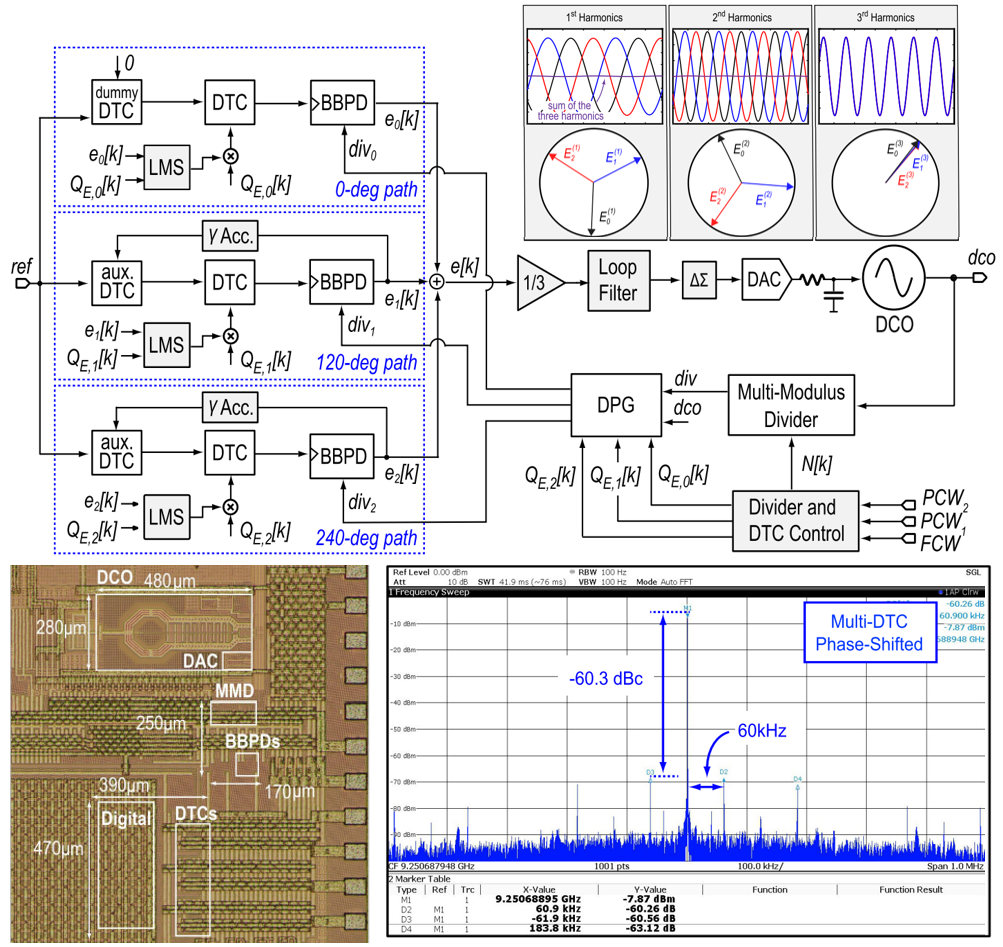

Pietro Salvi will present:

“A –66dBc Worst-Fractional-Spur and 58fs-Jitter Fractional-N Digital PLL Using a Supply-Resilient Pseudo-Differential Inverse-Constant-Slope DTC.”

We look forward to meeting you there!