List of designed, tested and published ASICs:

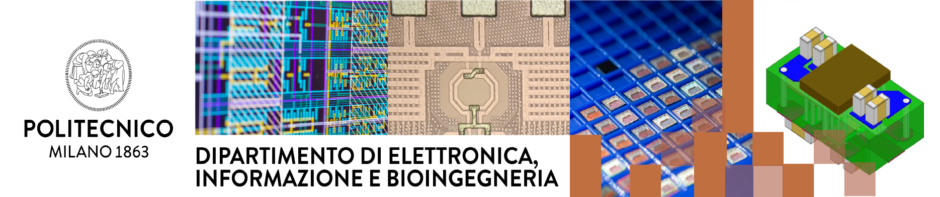

2-GS/s TI-ADC for 5G baseband (2022)

2-GS/s Time-Interleaved ADC in TSMC 28nm CMOS based on SAR ADC with on-chip digital calibration.

Dual Mode buck converter (2022)

Dual Mode buck converter with constant bandwidth time-based control and 20uA quiescent current for industrial applications.

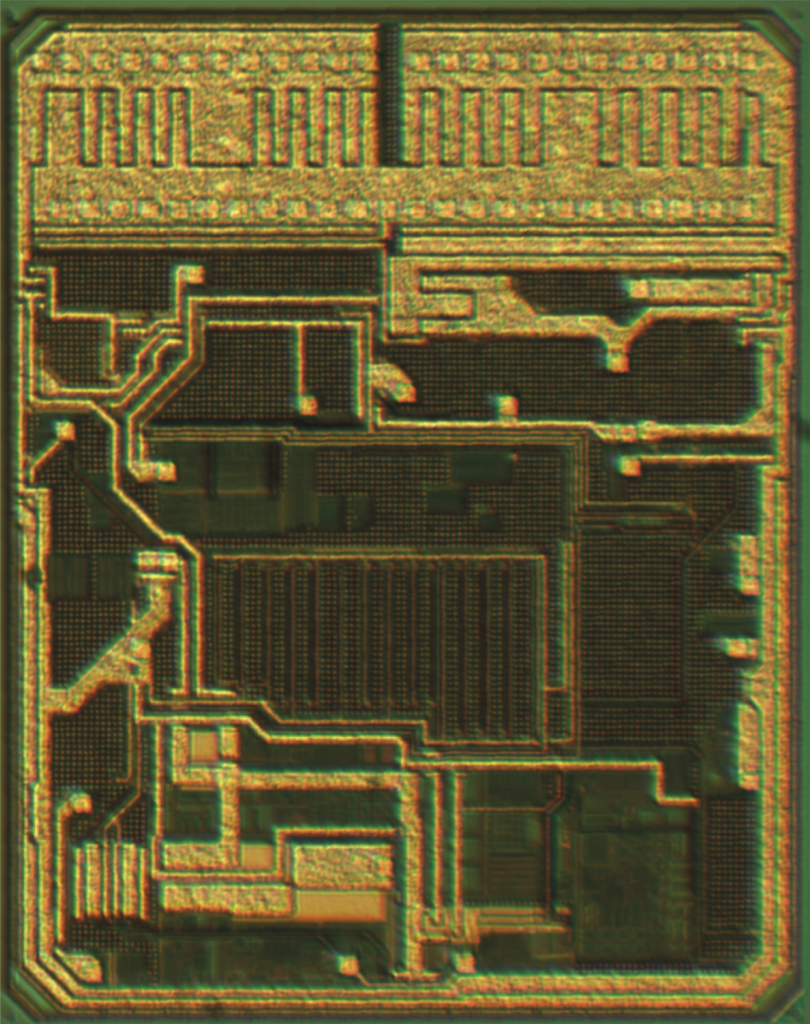

1-GS/s TI-ADC for 5G baseband (2021)

1-GS/s Time-Interleaved ADC in TSMC 28nm CMOS based on SAR ADC with on-chip digital calibration.

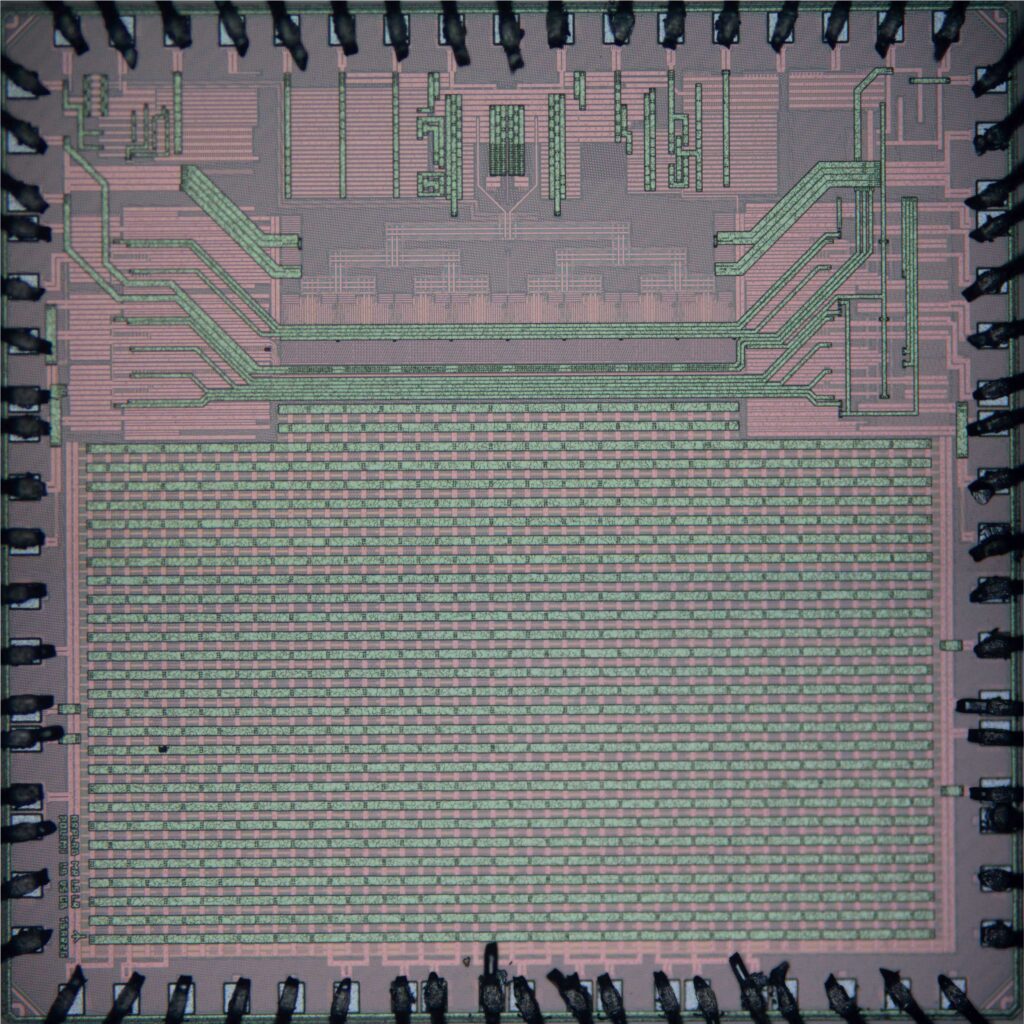

Time-based boost converter with RHP zero elimination. (2020)

Integrated boost converter with time-based control and RHP zero elimination in STM BCD8sp for AMOLED application.

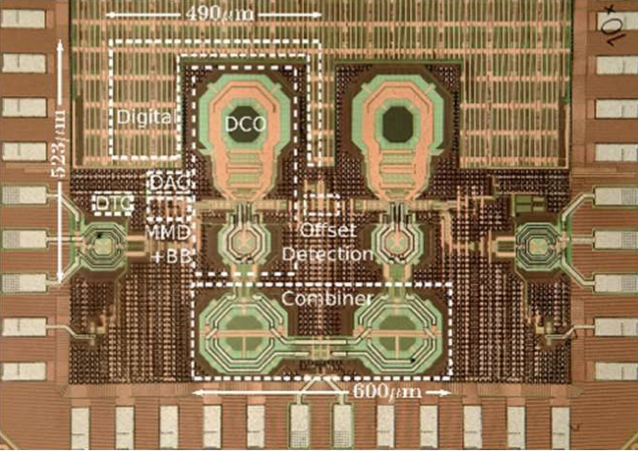

12.9-to-15.1GHz PLL-Based LO Phase-Shifting System (2020)

12.9-to-15.1GHz LO-generation system prototype in TSMC 28nm CMOS based on a double bang-bang digital fractional-N PLL with a 19-bit resolution programmable phase shift between the two outputs.

A 14GHz Fast lock Bang-Bang Digital PLL (2019)

Bang-bang digital PLL prototype in TSMC 28nm CMOS with 12.8-to-15.2-GHz output frequency range and a settling time below 20us .

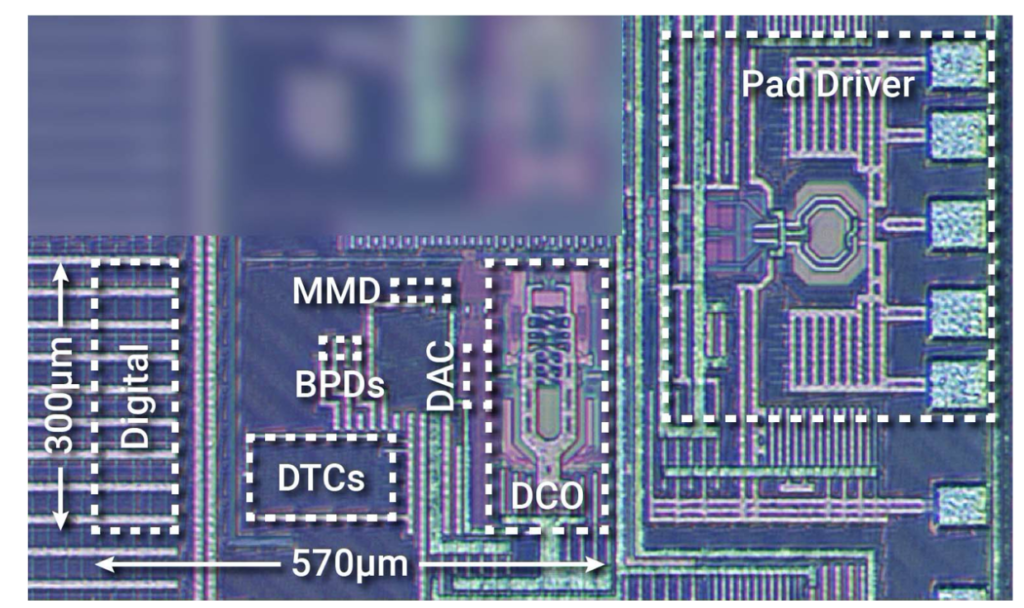

A 12.5GHz Fractional-N Type-I Sampling PLL (2019)

Analog sampling factional-N type-I PLL prototype in TSMC 28nm CMOS with 12.5-GHz output frequency, achieving 58fs of output signal integrated jitter.

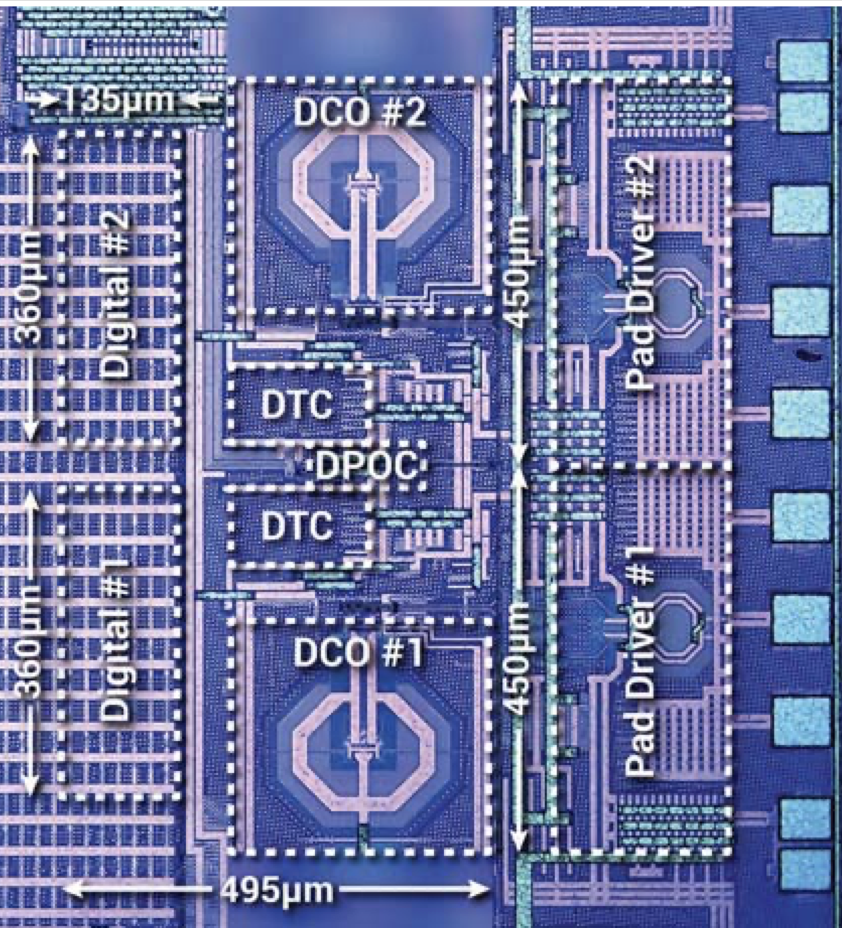

20GHz Dual-Core Digital PLL (2018)

Two-core bang-bang digital PLL prototype in STMicroelectronics 55nm BiCMOS process with second harmonic extraction and on-chip power combination.

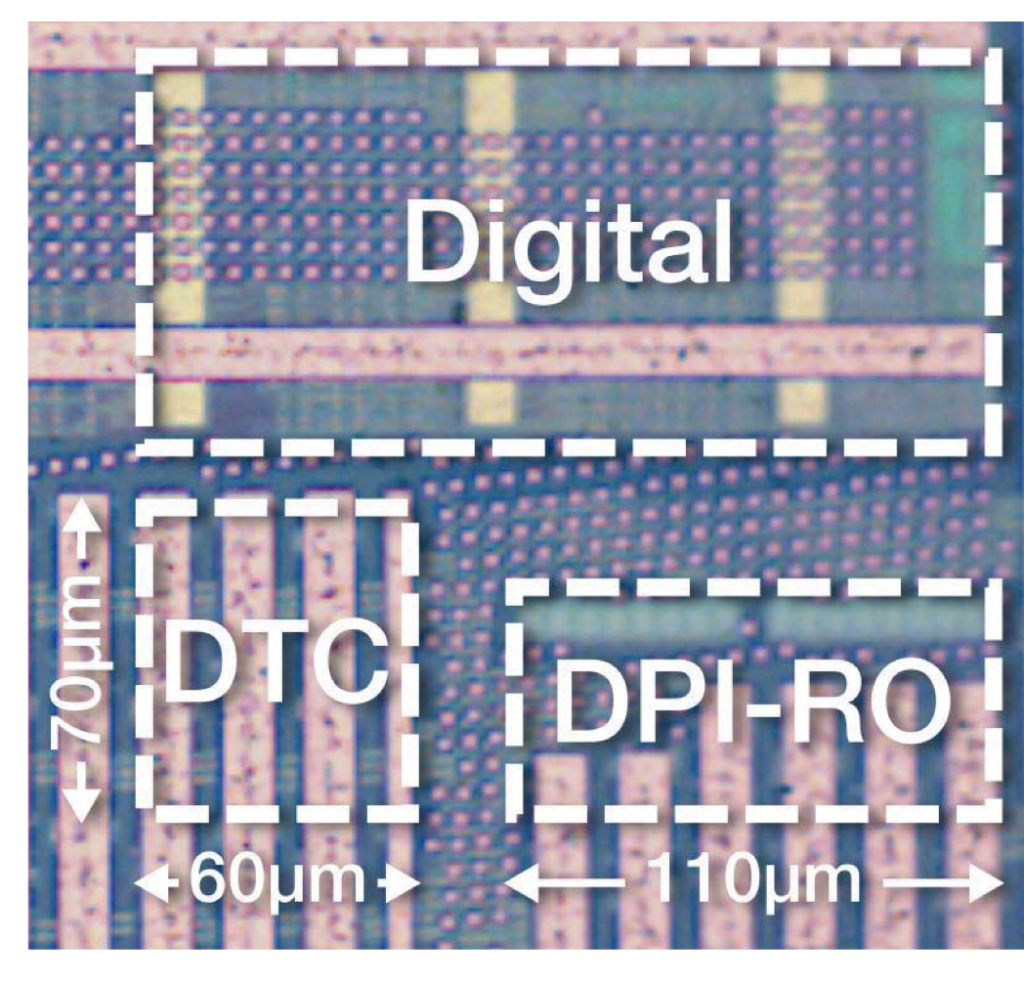

2.4GHz Digital MDLL (2017)

Bang-bang sub-sampling digital MDLL prototype in TSMC 65nm CMOS with DTC range reduction technique at 2.5mW power consumption.

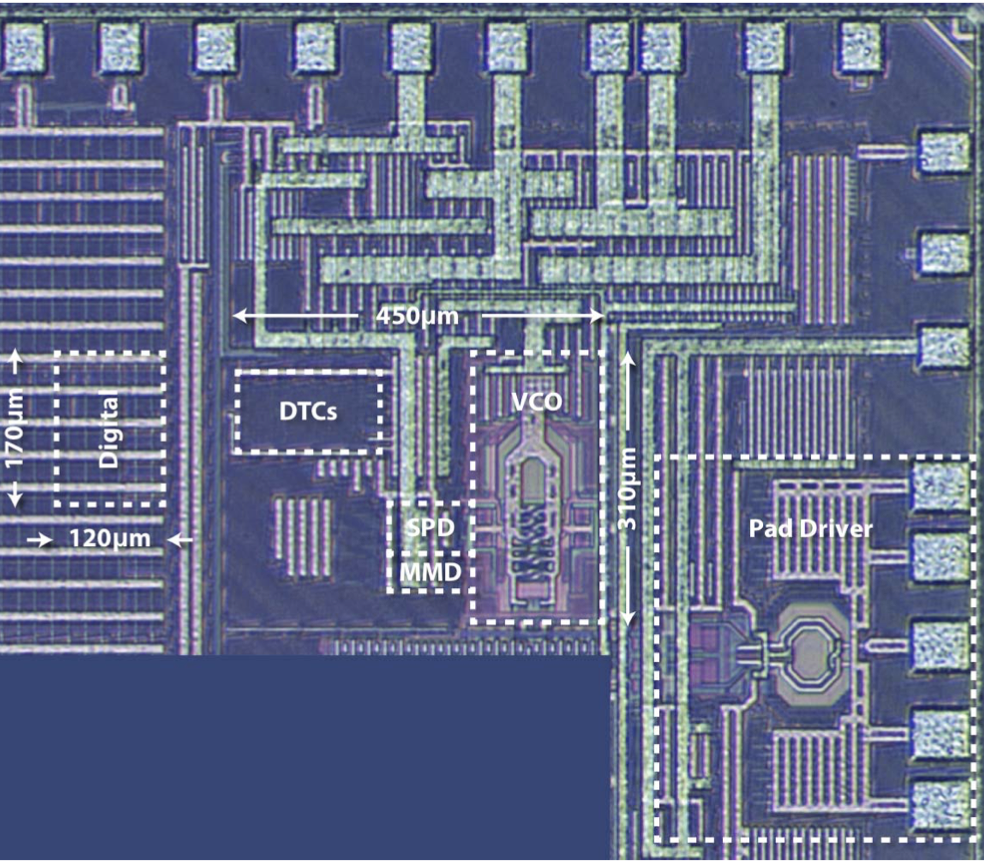

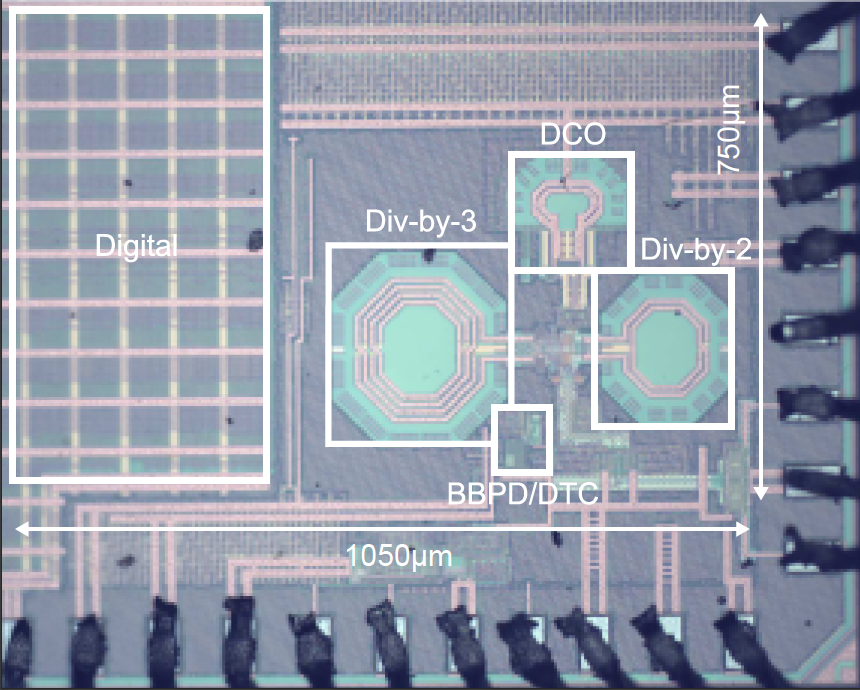

30-GHz Digital PLL (2017)

Bang-bang sub-sampling digital PLL prototype in TSMC 65nm CMOS with 30GHz Oscillator, Injection Locking divider by 6, 5-GHz output frequency, and chirp modulation.

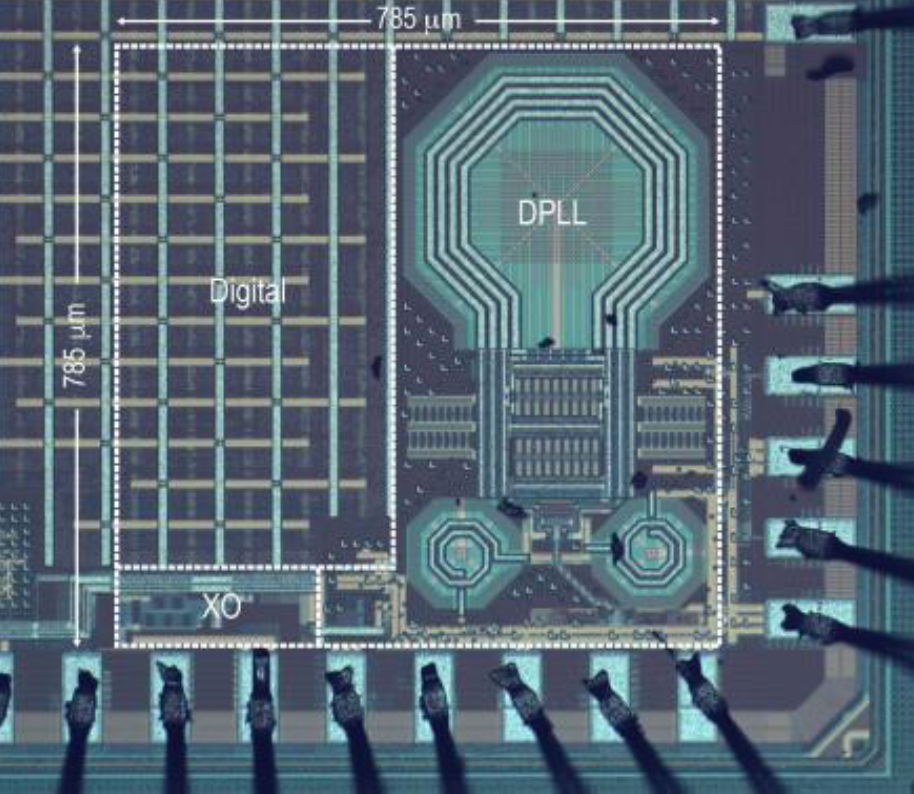

3.7-GHz Digital PLL (2016)

Bang-bang digital PLL prototype in STM 65nm CMOS process with 3.7-GHz output frequency, fast frequency hopping, phase-noise level compliant with GSM requirements. [1]